基于高速串行总线SRIO 的数据传输

基于高速串行总线SRIO 的数据传输

王 磊 王辉球 中电集团第二十研究所 陕西西安 710068

【文章摘要】

在综合化系统中,背板上模块之间通信速率的不同及交换信息数量的增加成为制约系统性能的瓶颈。为满足系统设计要求,本文提出了基于高速串行总线SRIO 的数据传输方案, 介绍了SRIO 总线协议及FPGA 实现, 设计实现了一种基于该传输方案的原理框图和具体方法,并且在负责研制的某型号综合化系统中验证了其可行性。

【关键词】

软件无线电;串行RapidIO ;FPGA

【Abstract】

In the integrated system,the different rate of communication and the amount of information exchanged between the modules on the backplane become the bottleneck of restricting the performance of the system.To meet the requirements of system design,this paper presents a data transmission scheme based on SRIO high-speed serial bus,describes the SRIO bus protocol and the FPGA implementation, designs a kind of principle block diagram and the specific method based on the transmission scheme and verifies its feasibility in charge of the development of a certain type of integrated system.

【Key words】

SDR(Software Defined Radio);SRIO ; FPGA

0 引言

随着信号处理技术的发展、芯片技术的成熟以及软件无线电技术的广泛使用和发展,无线电系统正在从功能设备逐渐堆积式的发展模式向综合化和通用化的发展模式转变。软件无线电的核心设计思想是在通用化的硬件平台上,通过不同的软件配置实现多种通信功能。随着系统中功能模块集成度的增强及信息传输量的急剧增加,对模块间互连接口的带宽、实时性及灵活性的要求越来越高,系统总线的可靠设计已经成为综合化系统的关键技术。

高速串行Rapid IO(即SRIO)总线技术采用包交换互连技术,具有高带宽、低时延和高性能编码等特点,满足了飞速发展的通信技术对系统性能的苛刻要求;采用串行拆分模拟信号技术满足了系统对管脚数量的限制以及对背板传输的要求;灵活的点对点等互连方式和软件可编程的传输速度能满足多种不同速率应用的需求。

1 SRIO 协议简介及FPGA 设计实现

1.1 SRIO 协议简介

SRIO 总线是一种开放式的基于包交换的高速串行标准总线,协议采用三层分级体系结构。逻辑层规范位于最高层,定义全部协议和包格式,为端点器件发起和完成事务提供必要的信息。传输层规范在中间层,定义SRIO 地址空间和在端点器件间传输包所需的路由信息。物理层规范在整个分级结构的底部,包括器件级接口的细节,如包传输机制、流量控制、电气特性和低级错误管理等。

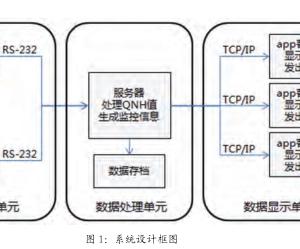

SRIO 的传输操作采用请求和响应机制,包(PACKET)是系统中端点器件的通信单元。由发起者(initiator)产生一个传输请求,请求包被传输到相邻的交换器件, 从而进入交换机构,通过交换机构这个完整的请求包被传输到目标器件(target),目标器件根据请求完成相应的操作后,发送相应的响应包,经过交换机构传回到发起者,这时一个完整的传输过程完成,流程如图1 所示。控制符一般在物理层互连中用作传输管理,如包的确认、流控信息和维护功能等。

1.2 SRIO 的FPGA 实现

系统的接口芯片采用Xilinx 公司的FPGA XC5VLX110T,其内置了16 个Rocket IO 收发器,支持从100Mbps 到3.75Gbps 串行数据传输速率,支持目前流行的包括Rapid IO 在内的高速串行I/O 接口标准。Rapid IO IP 核由物理层核,逻辑传输层核、缓冲器核和参考设计4 个部分

图1 SRIO 传输操作流程框图

图2 SRIO 逻辑层和传输层接口

组成。

逻辑层通过Xilinx 特有的本地Link 接口与物理层相连,以构成Rapid IO节点。逻辑层分为几个模块来控制发送和接收包的串接和解析,接口框图如图2 所示。其中用户接口(User Interface)包含4 个端口 (Initiator Request, Initiator Response, Target Request 和Target Response) ,从这里向remote 节点发送包或接收remote 节点发送的包,它是使用Xilinx SRIO 解决方案时用户通信使用的接口,还可以从这些端口发起到本节点配置寄存器的读写操作。维护接口包含2 个端口(Maintenance Request/Response Port 和Configuration Register Port),控制对逻辑层的配置寄存器以及用户定义寄存器或物理层配置寄存器的读写。

SRIO 的逻辑层业务最常使用直接IO/DMA 的传输方式,其包含多种传输格式。其中,SWIRTE 是最高效的传输格式, 但采用这种格式时,数据长度必须是8 字节的整数倍,带响应的写操作或读操作效率则最低,一般只能达到不带响应时传输效率的一半。在本系统中,采用SWRITE 格式。

在生成的SRIO IP 模块的顶层文件加入FIFO,将对外的数据接口由64bit 转为16bit,以便中频数据流的传输,并添加复位程序、接口时序等处理程序。由于产生的文件比较多,不利于程序的移植与维护,因此对功能测试正确的SRIO 模块进行封装,将封装后的接口模块和ngc 文件添加到工程即可,封装后的接口模块如图3 所示。其中,SRIORstnOver 为低时表明总线在进行复位,SRIOPort0InitOver 和SRIOPort1InitOver 表示一个bank 中的两路SRIO 总线链路建立完成, SRIOByteLen1 和SRIOByteLen2 表示两路SRIO 总线包的字节长度(设置为256), TxData1、TxData2、RxData1、RxData2 为两路SRIO 总线收发数据接口。

系统加电初始化完成后,只有检测到SRIOPort0InitOver 和SRIOPort1InitOver 为高电平时,才能通过相应的SRIO 链路进行数据收发。在系统工作过程中, 一旦检测到SRIOPort0InitOver 或者SRIOPort1InitOver 信号为低,则表明相应的SRIO 链路断开,需要对SRIO 模块进行复位,重新对链路进行握手通信,直到SRIOPort0InitOver 或者SRIOPort1InitOver 信号为高后才能通过SRIO 总线进行数据收发。

2 系统平台验证

采用封装好的SRIO 模块,在某综合化系统中实现了数据的正确传输,系统框图如图4 所示。主要包括显控CMU(数据综合处理单元)模块、交换模块、信号处理

图4 系统框图

图3 封装后的SRIO 模块接口

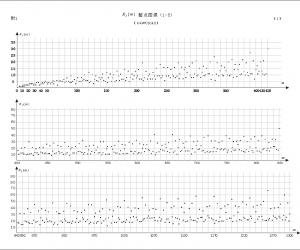

图5 数据传输测试结果图

器模块和变频模块。显控CMU 模块主要完成与PC 端控制命令及数据的交互,交换模块主要功能是根据从CMU 模块接收到的控制命令去切换变频模块与信号处理器模块之间的SRIO 链路。信号处理器模块主要是通过交换模块给变频模块传递滤波器带宽、频率、增益控制等参数,并对接收的信号进行处理。变频模块主要是根据接收到的控制指令设置模拟信道参数和传送波形数据。每个模块都采用本板时钟,为了保证中频数据通过SRIO 正确传输,信号处理器模块产生一个40MHz 的同步时钟传递给变频模块,即图4 中的LVDS 离散控制信号。

系统中频数据的传输不添加包头,进行点对点的直接传输。控制命令、带宽、频率等的传输采用包格式,通过包头对数据类型进行区分,比如传输频率码时,首先发送包头FFF0,然后设置状态信息和频率码,最后添加包尾0FFF。变频模块接收到FFF0 后,将接收到的频率码写入本地双口RAM,检测到0FFF 时表明频率码数据写入完成,然后根据状态信息对收发信道的频率码进行设置,测试结果如图5 所示。其中,(a)为信号处理器模块发送数据时序, (b)为变频模块接收数据时序,通过对比测试结果,可以验证数据传输的正确性。

3 结论

本文提出了基于SRIO 总线协议的数据传输方案,目的是在综合化系统中实现不同带宽、不同速率数据的实时稳定传输,并在系统中采用该传输方案实现了多种波形功能和控制命令字的传输,解决了SRIO 总线下波形信号同步传输及处理问题,解决了波形并行信号总线要求对综合化系统串行总线通用化的瓶颈问题。同时SRIO 协议的传输速率可通过软件升级, 有利于未来宽带波形扩展。

【参考文献】

[1]LogiCORE IP Serial RapidIO v5.6 User Guide[M] Xilinx Corporation,2011

[2]Zhang Feng, Wu Qin zhang, Ren Guo qiang, A highspeed serial transport platform based on SRIO for highresolution image[J]. Opto-Electronic Engineering, 2011,37(10):89-92.

[3] 冯华亮. 串行RapidIO: 高性能嵌入式互连技术. 今日电子, 2009, 9(9): 78-80

[4] 王勇, 林粤伟, 吴冰冰.RapidIO 嵌入式系统互连[M]. 北京: 电子工业出版社,2006